# FROM LAYOUT TO SCHEMATIC USING PATTERN RECOGNITION IN MICROWAVE COMPUTER AIDED DESIGN

S. Tadjiky and R.H. Jansen

Aachen University of Technology (RWTH), Dept. of El. Engineering, ITHE,

Kopernikusstr. 16, D-52074 Aachen, Germany

## ABSTRACT

A novel pattern recognition tool has been developed to interpret a given MIC/MMIC layout in terms of even complex library components. This allows to go from layout to the data needed for a schematic. It opens the way to automate design flow between different simulators via schematic and netlist level.

## INTRODUCTION

The common point of any kind of MIC/MMIC analysis and design is the layout, whether electromagnetic simulation or network theory-based analysis is used. As a step towards design automation, commercial electromagnetic simulators are capable, for example, to read layouts in various formats and then process this input by automatic gridding etc. to generate the necessary start-up file for the EM simulator [1]–[4]. However, such automated processing towards a netlist file or an equivalent schematic is not yet available to the authors' knowledge, when it comes to generating from the layout the necessary data for an analysis using network theory-based CAD packages. The reason for this is, that this requires the identification of geometrically complex components and identify those in an existing library of physic-oriented components, a foundry library, etc. The widely used practice in the microwave designer community is to manually segment a layout and associate with each of the resulting components a library name or electrical description. Note, that we are not describing here the automated extraction of RLC circuit elements and creation of a spice netlist. Such RLC extraction is done on the basis of computed electromagnetic results of a distributed structure in order to allow an equivalent circuit representation. The paper presented here, does not use simulation results, but pure pattern recognition to move from layout to schematic.

## PATTERN RECOGNITION

Based on previous work on a Design Assistant [5], that had already limited pattern recognition features, the respective capabilities have now been upgraded and extended in such a way, that not only elementary geometrical structures can be recognized, but also geometrically complex physical components, as they can be seen in a MMIC layout. An example for this is the recognition of spiral inductors and MIM capacitors, and the association of these components with the correct name of a library modul and with the complete set of recognition parameters. In the following, the main features of the recognition and identification algorithm are outlined and demonstrated by an example.

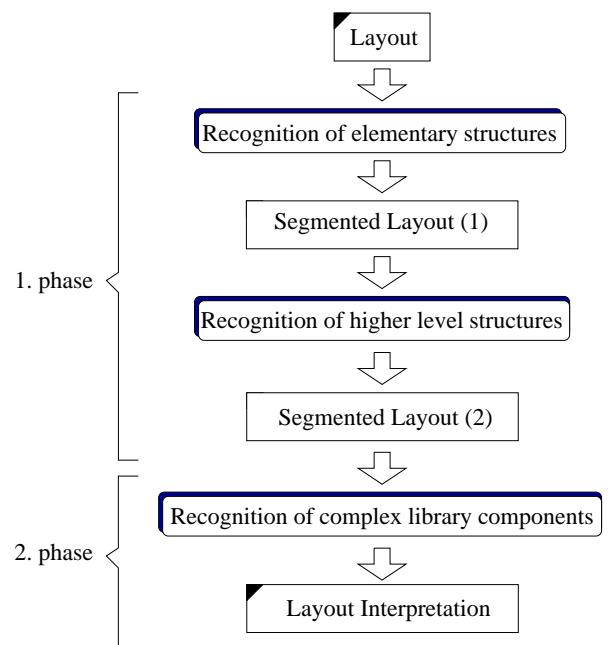

Fig. 1: The structure of pattern recognition

As is state-of-the-art practice in pattern recognition, the identification of structures of an image and the interpretation are performed in two phases. In the first phase, called “low level processing”, the processing of the image and the identification of elementary features are performed by the generation of a segmentation. In the second phase, the so-called “high level processing”, the content of the image is appropriately interpreted [6, 7]. While elements of low level processing have already been part of the tool described in Ref. [5], the extension and further development of the tool includes now the recognition of geometrically complex structures as library components and the assignment of individual parameters. In addition, the low level phase has been suitably modified. Fig. 1 visualizes the individual steps of the pattern recognition outlined here.

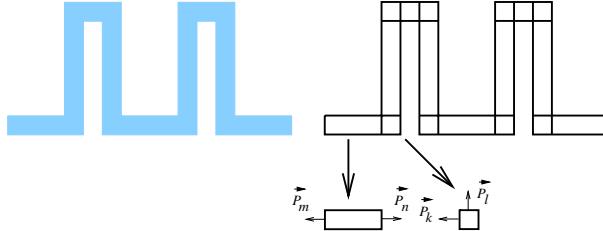

The algorithm is organized in three hierarchical levels. In the first level, layout geometry is partitioned in terms of elementary structures, like rectangles and triangles, which are still purely geometrical structures themselves. In order to identify these elements as elementary physical circuit structures, like sections of microstrip lines and bends, further interpretation is needed. We use for this the relative arrangement and direction of the neighbouring elements, which allows to associate features with the elements, like ports and port directions. This is illustrated by an example in Fig. 2.

**Fig. 2:** Recognition of elementary structures

Based on this first step, a first symbolic description of the layout and a first classification are achieved. The result of this first level is a segmented layout, characterized in terms of elementary layout structures. This already can be used as a basis for simulation with suitable simulators, as was described in Ref. [5].

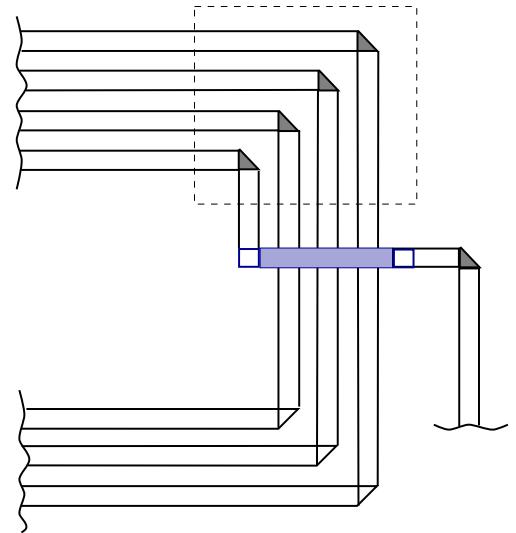

The second step or level of Fig. 1 consists in associating and grouping elementary structures to form higher level structures of intermediate complexity, like coupled strips and coupled bends incorporating the electrical coupling effects between basic elements. Note, that this arranging and grouping needs already some experience and expert knowledge implementation, but also needs to take into account the capabilities of the simulator to be addressed. The recognition of the outlined features is performed here by a di-

gital search scheme and is briefly described here by means of a simple example (s. Fig. 3).

**Fig. 3:** Recognition of coupled bends in a spiral inductor

The recognition procedure of coupled bends summarised and simplified is:

- Searching for corners with the same orientation (using port directions)

- Testing for corner matching criteria (2D-sorting)

- Grouping by examination of corner sequence (efficient implementation using binary search)

Figure 3 shows a part of a spiral inductor. As one can see, there are five hatched corners with the same port directions. Following the above mentioned 3 steps, the system recognises the group as 4 coupled bends (s. dotted lines).

Following this second level segmentation and classification, a representation of the considered structure exists in the form of a layout segmented into a level of grouped elements as outlined.

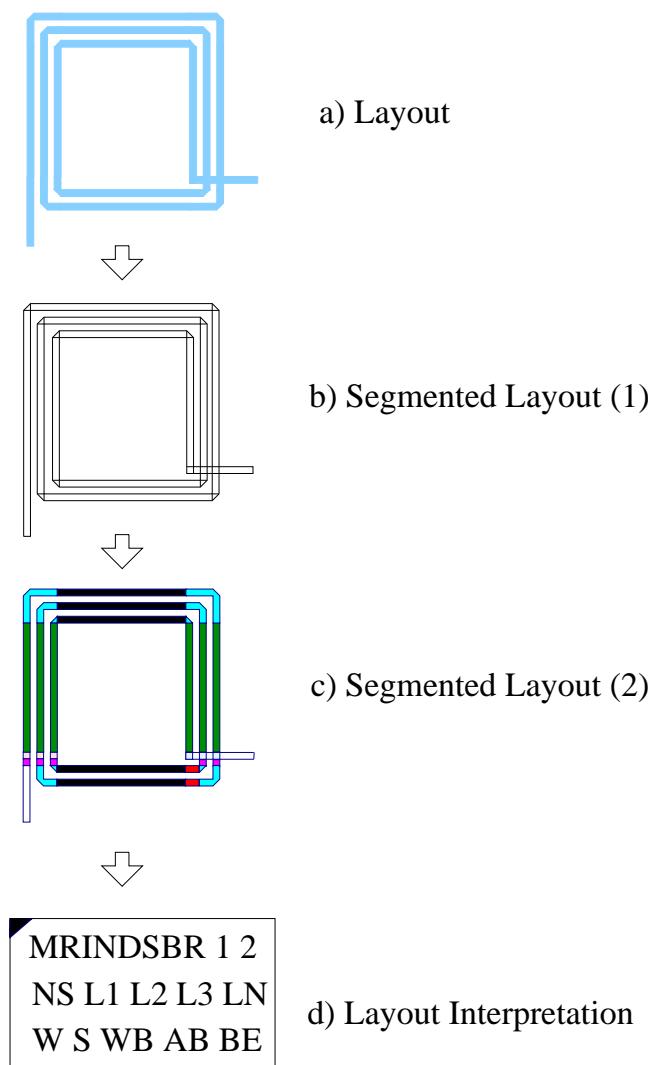

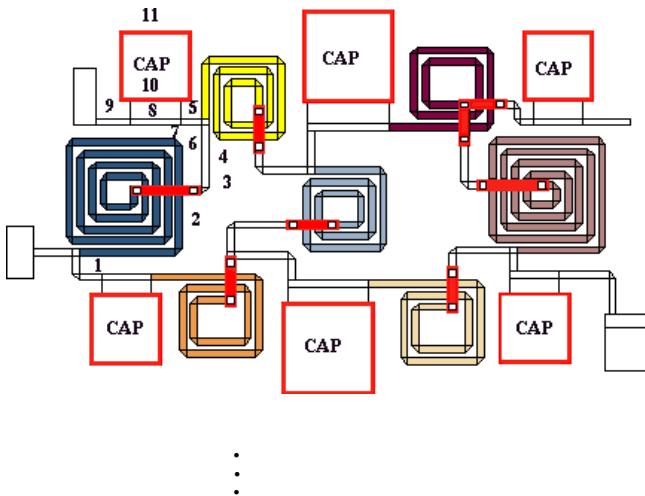

The third step and level now includes the so-called “high level phase” with symbolic processing, in order to identify complex components within the segmented layout. Following classification, the respective components are assigned symbolic names. This symbolic processing is again a grouping of the low level entities, which satisfy certain relations to form a more complex set. Fig. 4 illustrates the 3-step processing of Fig. 1 again by means of a simple example, starting from layout and arriving at a Touchstone format description containing the component name and the physical parameters NS, L1, L2, L3, LN, W, S, WB, AB and BE.

By this identification the component is uniquely described, given the fact, that the generated Touchstone description has a clear association with an existing CAD library. This kind of automated Touchstone file generation is considered as the basis to automatically move from one layout to several network theory-based simulators and associated libraries. It will also allow to move between those simulators if respective name conventions for library modules are agreed upon.

**Fig. 4:** Recognition of spiral inductors

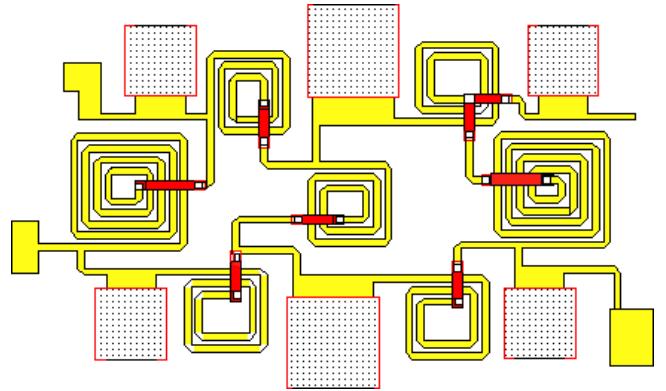

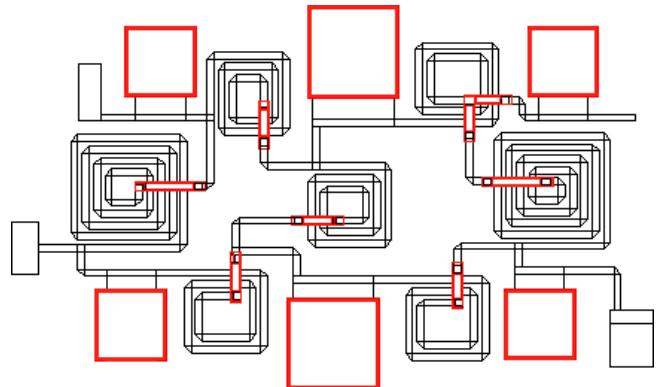

As a more complex example, the automated processing of the layout of a MMIC low pass filter example is considered. This was made available by Dassault Electronique in France as a test case [8]. Fig. 4a shows the layout of the considered MMIC filter with the prober pads, grounding structure at the chip edges and some other details removed for the sake of simplification. Fig. 4b shows the same layout following the first step of the algorithm depicted in Fig. 1.

**Figure 4a:** Layout of MMIC test filter

**Figure 4b:** Segmented Layout (1)

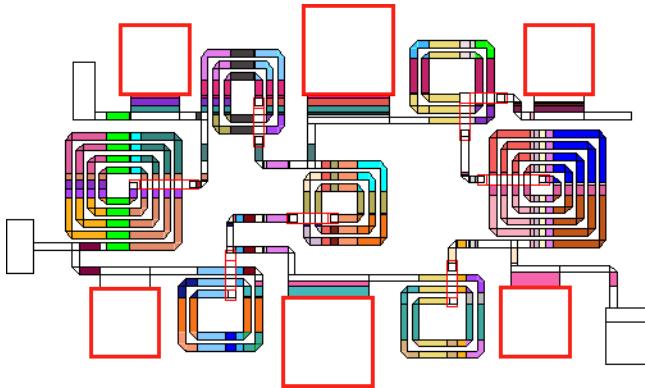

The second level of processing with grouped elementary structures is shown in Fig. 4c. Finally, the identification of complex geometrical entities, like spiral inductors and MIM capacitors, is visualized in Fig. 4d. The generated Touchstone description, which allows to invoke a schematic capture, is attached at the bottom of Fig. 4d.

## Conclusion

An algorithm has been developed in the context of the development of a Design Assistant for microwave CAD, which allows to move directly from layout to a schematic associated with library component modules via pattern recognition without previous electrical simulation. This represents a new step towards microwave design automation, towards the re-use of layouts for comparative investigation with different simulators and towards the interoperability of microwave design packages.

Figure 4c: Segmented Layout (2)

MRINDSBR 1 2 NS=18 L1=0.14 L2=0.155 L3=0.155 LN=0.016

W=0.01 S=0.006 WB=0.014 AB=90 BE=0.011

MBEND2 2 3 W=0.01

MLIN 3 4 W=0.01 L=0.087

MTEE 5 4 6 W1=0.01 W2=0.01 W3=0.01

MLIN 6 7 W=0.01 L= 0.03

MTEE 7 9 8 W1=0.01 W2=0.07 W3=0.01

MLIN 8 10 W=0.07 L=0.024

TFC 10 11 W=0.07 L=0.07 CO=0.0 DO=0.0

(All dimensions in millimeters)

Figure 4d: Layout Interpretation including part of the generated Touchstone file

- [1] R. H. Jansen. "Computer-aided design of microwave and millimeterwave ICs - Progress during the last decade and future perspectives", Invited Paper and Associated Viewgraphs. *Proc. 25th European Microwave Conference*, Bologna, Italy, 1995, 93–100.

- [2] Momentum, Product Sheet, Hewlett Packard, USA, Sept. 1993, 5091-8189E.

- [3] Microwave Explorer, User's Guide, Compact Software, 201 McLean Blvd, Paterson, New Jersey 07504 USA, Oct. 1995.

- [4] Sonnet Software, EM CAD Tools Overview, Liverpool, NY, USA, May 1995.

- [5] S. Tadjiky, R. H. Jansen. "(M)MIC Analysis using a hierarchy of simulation tools controlled by layout pattern recognition and expert knowledge". *IEEE MTT-S Int. Microwave Symp. Digest*, San Francisco, CA, U.S.A., 1996, 741–744.

- [6] C.E. Liedtke, M. Ender. *Knowledge-based Image Processing* (in German), Springer Verlag, Berlin; Heidelberg; New York, 1989.

- [7] H. Bunke H. Niemann. *Artificial Intelligence in Image and Speech Analysis* (in German), B.G. Teubner, Stuttgart, 1987.

- [8] Ph. Duême, Dassault Electronique, France, Private Communication, March 1996.